电子所高电源抑制比电压基准源设计技术研究获进展

李承蓬 许维胜 王翠霞

摘 要: 在此通过对带隙基准电压源电路进行建模分析,针对逆变电路的中低频使用环境,设计了一个应用于高压逆变器电路中的高电源电压抑制比,低温度系数的带隙基准电压源。该电路采用1 μm,700 V高压CMOS工艺,在5 V供电电压的基础上,采用一阶温度补偿,并通过设计高开环增益共源共栅两级放大器来提高电源电压抑制比,同时使用宽幅镜像电流偏置解决因共源共栅引起的输出摆幅变小的问题。基准电压源正常输出电压为2.394 V,温度系数为8 ppm/℃,中低频电压抑制比均可达到-112 dB。

关键词: 高电源电压抑制比; 带隙基准; 基准电压源; 低温度系数; 一阶补偿

中图分类号: TN432?34 文献标识码: A 文章编号: 1004?373X(2014)06?0132?04

0 引 言

基准电压源模块因其输出稳定,与电源电压、温度等变化无关,广泛应用于模拟和数模混合电路中,例如A/D,D/A转换器,逆变器等[1]。应用于高压逆变器中的基准电压源,为其他模块提供偏置电流和作为比较器等的基准电压使用,对此要求其在温度和电压变化的时候仍能保持其输出电压稳定,否则会引起电路出现逻辑混乱,使系统不能正常工作,甚至发生过压击穿等事故。这样在高压中低频环境下需要一个有良好温度系数和高电源电压抑制比的基准电压源的重要性就不言而喻。

传统的基准电压源在0~70 ℃的温度范围内产生温度系数为1×10-4[/°C]的基准电压,电压抑制比在-80~

-70 dB,且随着频率升高在103 Hz左右迅速下降,难以达到逆变器电路要求。本文采用无锡上华1 μm、700 V高压CMOS工艺进行设计与仿真,通过推导分析基准电压源电压抑制比的影响因数,对核心电路进行了改进并设计了一个高开环放大倍数,高电源抑制比的放大器,以减小温度系数并提高基准电压源的电压抑制比。此基准电压源的温度系数达到8 ppm/℃,交流低频电压抑制比达到-112 dB,并在中高频都能保持较高的电压抑制比。

1 改进的基准电压源电路

利用双极晶体管[Vbe]电压的负温度系数和不同电流密度偏置下两个双极晶体管电压差[Vbe]产生的正温度系数特性,可以获得零温度系数基准电压[2]。如图1所示,是经过改进的带隙基准电压源核心电路。使用两个双极晶体管并联来消除放大器失配的影响,用共源共栅电流源来保持每个支路的电流有相同的温度系数,并且利用共源共栅的电压屏蔽特性来解决因MOS管沟道长度调制所产生的对电源电压的依赖性[2?3]。

如图1所示,放大器工作在深度负反馈下,以保持[Va]和[Vb]相等,即[Va=Vb],同时[Va=2Vbe],[Vb=2Vbe3+IR2],可得到:

当T=300 K时,[?VBE?T=-1.5 mV/K],[?VT?T=+][0.087 mV/K]。此时,令双极晶体管Q3,Q4的发射极面积为Q1,Q2的N倍,I1,I2的电流为I3,I4的M倍,再适当选取[R1],[R2]的值,使[lnIC2AE3IS3AE2(1+R1R2)=1.5 mV/K0.087 mV/K≈17.2,]则可得到零温度系数输出电压[Vref]。

2 电源电压抑制比分析

启动电路和偏置电路对基准电压源的电源抑制比不产生影响,电源电压抑制比只与放大器和带隙基准核心电路有关,对于这两部分的结构如图2所示。

其中,[A1(s)]为放大器输入到输出的传递函数,即放大器的开环放大倍数,[V1]为放大器的输出,[Add(s)]为电源电压对放大器输出[V1]的传递函数,[A2_va(s)],[A2_vref(s)]分别为放大器的输出[V1]到端点a,[Vref]的传递函数,[Add_va(s)],[Add_vref(s)]为其相对应电源电压[Vdd]到a,[Vref]端的传递函数,[A3(s)]为[Vref]端到b的传递函数。

想要得到高电压抑制比的带隙基准电压源,除调整带隙基准核心电路器件参数外,还需要设计高开环增益、高电压抑制比的放大器,即[A1(0)]要大,[Add(0)]要小。

3 带隙基准源设计

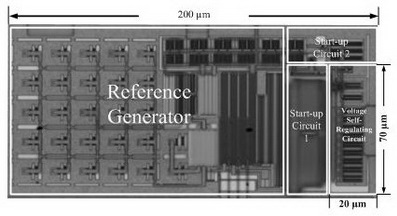

为了得到高电源抑制比的带隙基准源,设计如图3所示的带隙基准电压源电路。其中M1?M8及Q1?Q4组成带隙基准电路,M9?M32为本文设计的高开环增益、高电压抑制比的放大器。M23?M32构成运算放大器电路。为了提高增益采用两级放大。第一级为差分放大,使用共源共栅结构作为负载来提高增益。第二级采用共源级放大以继续提高增益,同时也扩展输出摆幅。C1为米勒电容,它使放大器的高频极点远离主要极点,保持放大器稳定工作,同时引入M30进行超前补偿,使放大器有足够的相位裕度。M9?M22构成偏置电路。因为使用共源共栅结构会限制输出摆幅,偏置电压的设计应尽量使共源共栅的每个MOS管都处于饱和区边缘,以使输出摆幅达到最大。所以设计的偏置电路采用宽幅电流镜来替代普通的电流镜,其提供的偏置电压能使共源共栅的每个MOS管都处于饱和区的边缘。图4中M9?M12和M20构成一个PMOS的宽幅电流源,M13?M16和M19构成一个NMOS宽幅电流源,M17,M18,M21,M22构成偏置电流环。

M33?M36构成启动电路。当电路中所有电流都为零时,M36处于截止状态,M33,M34的栅极为高电平,使其导通,启动电路。当电路启动后,M36导通将拉低M33,M34的栅极电压,使它们关断,从而不再影响电路。

如上文所述的设计可得到高开环增益的放大器,对于高电压抑制比的设计如下。对于两级放大器的电源电压抑制比,文献[5]给出了影响放大器电源抑制比的因素,在低频时[Add≈1],主要的影响因素为差分输入级尾电流的偏置电压[Vbias]随电源电压[Vdd]变化而引起的电流变化会使电源抑制比下降。所以在偏置电路的设计时要保证[Vbias]不受电源电压影响。对于偏置电路有[ID15=ID16],

通过所设计的偏置电路使M16的跨导只有几何比例和R0决定,与电源电压、工艺参数、温度等无关,且与M16在同一个偏置网络中的所有晶体管的跨导都会保持稳定。这样对于M23的[VGS]就可以保持不随电源电压变化,同时在设计时,适当增大M23的L,可增大M23的输出电阻,也可有效抑制电源电压的影响,这样可以保持尾电流不变,解决放大器在低频时随电源变化电源抑制比降低的问题。

4 电路仿真和测试

本次设计在5 V电源电压下,利用Cadence SPECTRE工具对基准电压源进行电路仿真。图4是基准电压源的温度特性曲线,在-45~100 ℃的温度范围内,基准电压变化幅度为0.002 8 V,温度系数为8 ppm/℃。

图5是基准电压源交流电源电压抑制比仿真曲线。在中低频部分的电源电压抑制比可以达到-112 dB。带隙基准电压源的测试结果如表1所示。

5 结 语

本文使用1 μm,700 V高压COMS工艺,通过对基准电压源进行建模分析,设计了一种高开环放大倍数和电源电压抑制比的放大器,从而得到了在中低频下高电源电压抑制比的基准电压源。在5 V电源电压供电情况下,该电路输出基准电压为2.394 V,温度系数8 ppm/℃,电源电压抑制比可达到-112 dB。

表1 带隙基准电压源测试结果

参考文献

[1] 应建华,陈嘉,王洁.低功耗、高电源抑制比基准电压源的设计[J].半导体学报,2007,28(6):975?979.

[2] JOHNS D A, MARTIN K. Analog integrated circuit design [M]. 北京:机械工业出版社,2005.

[3] 张朵云.高电源抑制CMOS基准源的设计[D].南京:东南大学,2006.

[4] SUN N, SOBOT R. A low?power low?voltage bandgap reference in CMOS [C]// Proceedings of 2010 23rd Canadian Conference on Electrical and Computer Engineering. Calgary, Canada: [s.n.], 2010: 1?5.

[5] 周玮,吴贵能,李儒章.一种高电源抑制比CMOS运算放大器[J].微电子学,2009,39(3):340?343.

[6] VAJPAYEE P, SHRIVASTAVA A. Wide output swing inverter fed modified regulated cascode amplifier for analog and mixed?signal [C]// Proceedings of TENCON 2009 IEEE Region 10 Conference. Singapore: IEEE, 2009: 1?5.

[7] 朱治鼎,彭晓宏,吕本强,等.高性能折叠式共源共栅运算放大器的设计[J].微电子学,2012,42(2):146?149.

[8] HEYDARI B, REYNAERT P. A 60 GHz 90 nm CMOS cascode amplifier with interstage matching [C]// Proceedings of Microwave Integrated Circuit Conference. Munich, Germany: [s.n.], 2007: 88?91.

[9] 周永峰,戴庆元,林刚磊.一种用于CMOS A/D转换器的带隙基准电压源[J].微电子学,2009,39(2):25?33.

[10] 史侃俊,许维胜,余有灵.CMOS带隙基准电压源中的曲率矫正方法[J].现代电子技术,2006,29(5):113?116.

通过所设计的偏置电路使M16的跨导只有几何比例和R0决定,与电源电压、工艺参数、温度等无关,且与M16在同一个偏置网络中的所有晶体管的跨导都会保持稳定。这样对于M23的[VGS]就可以保持不随电源电压变化,同时在设计时,适当增大M23的L,可增大M23的输出电阻,也可有效抑制电源电压的影响,这样可以保持尾电流不变,解决放大器在低频时随电源变化电源抑制比降低的问题。

4 电路仿真和测试

本次设计在5 V电源电压下,利用Cadence SPECTRE工具对基准电压源进行电路仿真。图4是基准电压源的温度特性曲线,在-45~100 ℃的温度范围内,基准电压变化幅度为0.002 8 V,温度系数为8 ppm/℃。

图5是基准电压源交流电源电压抑制比仿真曲线。在中低频部分的电源电压抑制比可以达到-112 dB。带隙基准电压源的测试结果如表1所示。

5 结 语

本文使用1 μm,700 V高压COMS工艺,通过对基准电压源进行建模分析,设计了一种高开环放大倍数和电源电压抑制比的放大器,从而得到了在中低频下高电源电压抑制比的基准电压源。在5 V电源电压供电情况下,该电路输出基准电压为2.394 V,温度系数8 ppm/℃,电源电压抑制比可达到-112 dB。

表1 带隙基准电压源测试结果

参考文献

[1] 应建华,陈嘉,王洁.低功耗、高电源抑制比基准电压源的设计[J].半导体学报,2007,28(6):975?979.

[2] JOHNS D A, MARTIN K. Analog integrated circuit design [M]. 北京:机械工业出版社,2005.

[3] 张朵云.高电源抑制CMOS基准源的设计[D].南京:东南大学,2006.

[4] SUN N, SOBOT R. A low?power low?voltage bandgap reference in CMOS [C]// Proceedings of 2010 23rd Canadian Conference on Electrical and Computer Engineering. Calgary, Canada: [s.n.], 2010: 1?5.

[5] 周玮,吴贵能,李儒章.一种高电源抑制比CMOS运算放大器[J].微电子学,2009,39(3):340?343.

[6] VAJPAYEE P, SHRIVASTAVA A. Wide output swing inverter fed modified regulated cascode amplifier for analog and mixed?signal [C]// Proceedings of TENCON 2009 IEEE Region 10 Conference. Singapore: IEEE, 2009: 1?5.

[7] 朱治鼎,彭晓宏,吕本强,等.高性能折叠式共源共栅运算放大器的设计[J].微电子学,2012,42(2):146?149.

[8] HEYDARI B, REYNAERT P. A 60 GHz 90 nm CMOS cascode amplifier with interstage matching [C]// Proceedings of Microwave Integrated Circuit Conference. Munich, Germany: [s.n.], 2007: 88?91.

[9] 周永峰,戴庆元,林刚磊.一种用于CMOS A/D转换器的带隙基准电压源[J].微电子学,2009,39(2):25?33.

[10] 史侃俊,许维胜,余有灵.CMOS带隙基准电压源中的曲率矫正方法[J].现代电子技术,2006,29(5):113?116.

通过所设计的偏置电路使M16的跨导只有几何比例和R0决定,与电源电压、工艺参数、温度等无关,且与M16在同一个偏置网络中的所有晶体管的跨导都会保持稳定。这样对于M23的[VGS]就可以保持不随电源电压变化,同时在设计时,适当增大M23的L,可增大M23的输出电阻,也可有效抑制电源电压的影响,这样可以保持尾电流不变,解决放大器在低频时随电源变化电源抑制比降低的问题。

4 电路仿真和测试

本次设计在5 V电源电压下,利用Cadence SPECTRE工具对基准电压源进行电路仿真。图4是基准电压源的温度特性曲线,在-45~100 ℃的温度范围内,基准电压变化幅度为0.002 8 V,温度系数为8 ppm/℃。

图5是基准电压源交流电源电压抑制比仿真曲线。在中低频部分的电源电压抑制比可以达到-112 dB。带隙基准电压源的测试结果如表1所示。

5 结 语

本文使用1 μm,700 V高压COMS工艺,通过对基准电压源进行建模分析,设计了一种高开环放大倍数和电源电压抑制比的放大器,从而得到了在中低频下高电源电压抑制比的基准电压源。在5 V电源电压供电情况下,该电路输出基准电压为2.394 V,温度系数8 ppm/℃,电源电压抑制比可达到-112 dB。

表1 带隙基准电压源测试结果

参考文献

[1] 应建华,陈嘉,王洁.低功耗、高电源抑制比基准电压源的设计[J].半导体学报,2007,28(6):975?979.

[2] JOHNS D A, MARTIN K. Analog integrated circuit design [M]. 北京:机械工业出版社,2005.

[3] 张朵云.高电源抑制CMOS基准源的设计[D].南京:东南大学,2006.

[4] SUN N, SOBOT R. A low?power low?voltage bandgap reference in CMOS [C]// Proceedings of 2010 23rd Canadian Conference on Electrical and Computer Engineering. Calgary, Canada: [s.n.], 2010: 1?5.

[5] 周玮,吴贵能,李儒章.一种高电源抑制比CMOS运算放大器[J].微电子学,2009,39(3):340?343.

[6] VAJPAYEE P, SHRIVASTAVA A. Wide output swing inverter fed modified regulated cascode amplifier for analog and mixed?signal [C]// Proceedings of TENCON 2009 IEEE Region 10 Conference. Singapore: IEEE, 2009: 1?5.

[7] 朱治鼎,彭晓宏,吕本强,等.高性能折叠式共源共栅运算放大器的设计[J].微电子学,2012,42(2):146?149.

[8] HEYDARI B, REYNAERT P. A 60 GHz 90 nm CMOS cascode amplifier with interstage matching [C]// Proceedings of Microwave Integrated Circuit Conference. Munich, Germany: [s.n.], 2007: 88?91.

[9] 周永峰,戴庆元,林刚磊.一种用于CMOS A/D转换器的带隙基准电压源[J].微电子学,2009,39(2):25?33.

[10] 史侃俊,许维胜,余有灵.CMOS带隙基准电压源中的曲率矫正方法[J].现代电子技术,2006,29(5):113?116.