基于数字锁相环的晶振频率同步模块设计

李二鹏 文开章 王煜

摘 要: 为解决普通晶振频率长期漂移量较大的问题,提出了一种用GPS秒脉冲对晶振脉冲在线自动测量及修正,从而产生本地高精度时钟的方法,据此设计了一种基于单片机和CPLD的智能自校准数字时钟系统。介绍了时钟产生及校准模块、鉴相及相差测量模块等硬件电路组成和数据采集、晶振误差补偿算法实现等软件设计。该系统在需要较高精度时间显示的场所具有实际应用价值。

关键词: GPS; 晶振时钟; 回归分析; CPLD

中图分类号: TN78?34; TP202 文献标识码: A 文章编号: 1004?373X(2014)19?0102?03

Design of high precision digital clock based on crystal oscillator compensation

LI Er?peng, WEN Kai?zhang, WANG Yu

(Northwest Institute of Nuclear Technology, Xian 710024, China)

Abstract: To resolve the long term existing problem of long drift distance of crystal oscillator frequency, a method of producing local high?accuracy clock by automatically detecting and correcting the crystal oscillator pulse by means of GPS second pulse on line is put forward. According to this means, a CPLD and MCU based digital clock system with intelligent auto?calibration was designed. The composition of the hardware circuits of clock production and emendation module, and phase discrimination and phase difference measurement module, as well as design realization of the software for data acquisition and the crystal oscillator error compensation are introduced. The system has the actual application value in the site of needing high?accuracy time display.

Keywords: GPS; crystal oscillator clock; regression analysis; CPLD

0 引 言

随着电子技术的飞速发展,国内外已大量地把FPGA/CPLD器件、微处理器、GPS定时校频等技术应用于高精度时钟的研究与设计[1?2]。一个时钟的准确与否主要取决产生秒脉冲的频率源准确度。高稳晶振和铷原子频标等设备产生的秒脉冲具有很高的频率准确度,但其造价昂贵;普通晶振的准确度虽然只有10-5左右,但因其累积误差具有良好的一致性[3],通过定时校频设备(长、短波接收机和GPS接收机)对其进行比对校准后,准确度会得到显著提高[4?5]。GPS高精度授时技术因其技术指标较高和造价较低被广泛应用。本文以GPS秒脉冲作为标准频率源,对晶振产生的秒脉冲进行比对测量,采用回归分析法对晶振累积误差数据进行数理统计[6],并对其秒脉冲在线自动修正,设计了一种易于实现、成本低廉且具有自校准功能的数字时钟系统。

1 数字时钟组成原理

基于频率补偿的高精度数字时钟由GPS定时接收机、普通晶振、鉴相及相差测量电路、时钟产生及校准电路、单片机数据算法处理模块等组成。系统组成如图1所示。

GPS定时接收机每秒输出1路TTL电平的标准秒脉冲(1 PPS),秒脉冲的时间信息数据通过RS 232串口输出(TTL电平),由单片机读取。晶振是本地秒脉冲产生和相差测量的频率源,时钟产生及校准电路产生本地原始秒脉冲及修正后秒脉冲。鉴相电路产生本地晶振和GPS秒脉冲相位差,相差测量电路采用脉冲填充计数法测量GPS秒脉冲与本地秒脉冲相位的差值[7],测量结果由单片机读取。单片机采用最小二乘法计算出相差修正值并传送给时间校准电路,校准本地秒脉冲与GPS精确同步。

时钟产生电路是1 Hz频率源,由晶振分频得到,精密调整分频系数可以获得高精度1 Hz频率信号。普通晶振标称频率与实际输出频率有误差且随时间产生累积,长期稳定性差而短期稳定性好。以GPS秒脉冲定时,用比时法测量晶振实际分频输出的1 Hz频率与GPS秒脉冲的相位差值,每秒测量一次,测量结果通过并行接口电路送入单片机的存储单元,单片机对采集到的一组相差值进行基于一元回归的最小二乘数理统计,计算出晶振误差估计值,通过调整晶振分频系数以校准输出频率。从而构造一种低成本的具有较高精度的本地时钟系统。

2 硬件电路设计

硬件电路模块设计均以可编程逻辑器件EPM7128SLC84的CPLD作为目标器件。软件为Altera公司的QuartusⅡ,采用Verilog HDL硬件描述语言设计模块功能[8]。

电路设计主要分为本地时钟产生及校准模块,鉴相及相差计数模块。

2.1 时钟产生及校准模块

时钟产生校准电路组成如图2所示,主要由24位计数器、预置值寄存器、比较器电路组成。

系统上电后,复位信号对24位计数器、24位预置值寄存器清零。以GPS秒脉冲上升沿作为首次计数的同步信号,开始对本地晶振计数。24位计数器计数值与预置初始频率值(11 059 200 Hz)比较,若不相等,继续完成计数操作,若两者相等,则对计数器清零,重新开始计数,这样通过对晶振分频就得到了本地秒脉冲信号。

由于晶振存在漂移误差,本地产生的秒脉冲不可避免的与GPS秒脉冲存在相位差,鉴相及相差计数电路每秒都会对两者的相位差进行提取并计数。一旦采集的相差数据达到单片机需要的数据量(在本系统中设计提取相差数据量为20个),则单片机采用最小二乘法对得到的数据进行统计计算,得到补偿后的频率值,并通过预置值寄存器送入CPLD,实现晶振频率修正。图3为用示波器观测到的波形。Ch1通道为GPS接收机输入的秒脉冲,Ch2通道为晶振产生的秒脉冲波形,Ch3通道为数据传输中断请求信号。

2.2 鉴相与相差计数电路设计实现

鉴相电路主要将GPS秒脉冲和晶振秒脉冲的相位差信号提取出来,作为相差计数电路的闸门信号。这里设计了3D鉴相器完成这一功能。

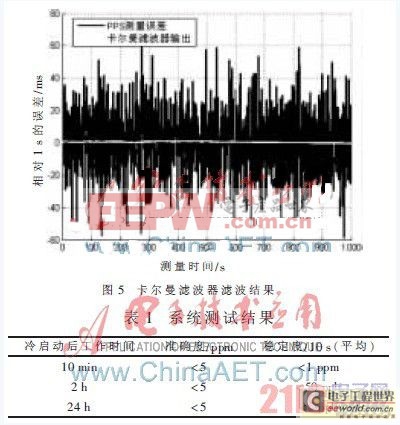

3D鉴相器使用3个D触发器和1个2选1选择器构成,以GPS信号作参考,分别在晶振秒脉冲前沿超前、滞后的情况下,以选择器A端、B端作为输出,S端作为晶振秒脉冲相位变化的标志。其电路组成如图4所示。时序仿真图如图5所示。

相差计数电路采用闸门法[9],以晶振脉冲作为计数填充脉冲对相差信号计数,并将计数结果保存在存储器中。晶振秒脉冲下降沿中断触发信号触发单片机响应中断,将相差数据读入单片机的内存单元,然后向CPLD计数器发出清零信号,对相差计数器清零,等待下一个相差信号的到来。

3 算法设计

软件设计所用器件为P89C51单片机,开发环境为Keil C51[10]。单片机实现最小二乘算法,具体实现方法如下:单片机接收相差数据到其设定数值时,将得到的数据按一元线性数理统计模型进行计算[3,6],得到模型系数[a,b]的估计值和需要补偿的计数值,通过数据总线将修正值送入CPLD的存储器修正晶振秒脉冲输出。单片机完成算法流程见图6。

4 相差数据算法处理及修正结果

表1给出了单片机实际采集到的一组相差数据。

基于一元回归方程的最小二乘算法得到了[a,][b]的估计值,其中,[a]为本地晶振产生的秒脉冲相对于GPS秒脉冲的初始误差,[b]为晶振秒脉冲每秒相对于GPS秒脉冲产生的频偏。从以上采集到的数据及[a,][b]估计值计算可知,本地晶振在补偿前相对于标准频率(以GPS为参考)的准确度为10-5,补偿后其准确度为10-8,且晶振频偏相对于标准频率具有很好的线性关系,通过调整晶振的分频系数,可有效提高晶振秒脉冲的准确性。

图7,图8给出了示波器在晶振秒脉冲校正前后观察到的波形。Ch1为GPS秒脉冲上升沿,Ch2为晶振秒脉冲上升沿,Ch3为相差。

从波形图看出,补偿之前,GPS与晶振秒脉冲在某时刻差约340 ms,并且这个差值因为晶振的漂移和其他误差的影响而不断增大。此时,单片机处于接收相差数据阶段,一旦达到其预定接收数值要求,单片机依据回归方程算出需要补偿的数值,对晶振时钟误差进行修正。从补偿的结果看,晶振秒脉冲和GPS秒脉冲的同步精度优于200 ns。

5 结 语

通过GPS自动定时校频,设计了数字式频率合成的高精度晶振时标。通过采用频率补偿方法,使本地普通晶振产生的时钟准确度由10-5提高到了10-8,获得了较好的补偿效果。守时性能主要取决于晶振的稳定性,若要提高守时性能,只需要在电路中采用更高稳定度的频率标准即可达到目标。

参考文献

[1] 张斌,张东来.基于GPS的高精度时钟在线校频与授时研究[J].中国电机工程学报,2012,32(10):160?167.

[2] 蓝波,胡修林.一种高精度系统时间同步方法[J].信息与控制,2011,40(3):61?65.

[3] 李二鹏,文开章,冯保红,等.石英晶体振荡器频率特性的测量与分析[J].测控技术,2010,29(1):81?83.

[4] NAOTO K, MASAHIRO S, TOHRU M, et al. Monitoring of interarea oscillation mode by synchronized phasor measurement [J]. IEEE Transactions on Power Systems, 2006, 21(1): 260?268.

[5] 刘利辉,增建平.100 MHz低噪声恒温石英晶体振荡器研制[J].湖南大学学报,2009,36(7):53?56.

[6] 费业泰.误差理论与数据处理[M].6版.北京:机械工业出版社,2010.

[7] 马凤鸣.时间频率计量[M].北京:中国计量出版社,2009.

[8] 吴继华.Altera FPGA/CPLD设计(高级篇)[M].2版.北京:人民邮电出版社,2011.

[9] 苗苗,周渭,刘晨,等.用于时间同步的高精度短时间间隔测量方法[J].北京邮电大学学报,2012,35(4):49?51.

[10] 蔡振江.单片机原理及应用[M].北京:电子工业出版社,2011.

系统上电后,复位信号对24位计数器、24位预置值寄存器清零。以GPS秒脉冲上升沿作为首次计数的同步信号,开始对本地晶振计数。24位计数器计数值与预置初始频率值(11 059 200 Hz)比较,若不相等,继续完成计数操作,若两者相等,则对计数器清零,重新开始计数,这样通过对晶振分频就得到了本地秒脉冲信号。

由于晶振存在漂移误差,本地产生的秒脉冲不可避免的与GPS秒脉冲存在相位差,鉴相及相差计数电路每秒都会对两者的相位差进行提取并计数。一旦采集的相差数据达到单片机需要的数据量(在本系统中设计提取相差数据量为20个),则单片机采用最小二乘法对得到的数据进行统计计算,得到补偿后的频率值,并通过预置值寄存器送入CPLD,实现晶振频率修正。图3为用示波器观测到的波形。Ch1通道为GPS接收机输入的秒脉冲,Ch2通道为晶振产生的秒脉冲波形,Ch3通道为数据传输中断请求信号。

2.2 鉴相与相差计数电路设计实现

鉴相电路主要将GPS秒脉冲和晶振秒脉冲的相位差信号提取出来,作为相差计数电路的闸门信号。这里设计了3D鉴相器完成这一功能。

3D鉴相器使用3个D触发器和1个2选1选择器构成,以GPS信号作参考,分别在晶振秒脉冲前沿超前、滞后的情况下,以选择器A端、B端作为输出,S端作为晶振秒脉冲相位变化的标志。其电路组成如图4所示。时序仿真图如图5所示。

相差计数电路采用闸门法[9],以晶振脉冲作为计数填充脉冲对相差信号计数,并将计数结果保存在存储器中。晶振秒脉冲下降沿中断触发信号触发单片机响应中断,将相差数据读入单片机的内存单元,然后向CPLD计数器发出清零信号,对相差计数器清零,等待下一个相差信号的到来。

3 算法设计

软件设计所用器件为P89C51单片机,开发环境为Keil C51[10]。单片机实现最小二乘算法,具体实现方法如下:单片机接收相差数据到其设定数值时,将得到的数据按一元线性数理统计模型进行计算[3,6],得到模型系数[a,b]的估计值和需要补偿的计数值,通过数据总线将修正值送入CPLD的存储器修正晶振秒脉冲输出。单片机完成算法流程见图6。

4 相差数据算法处理及修正结果

表1给出了单片机实际采集到的一组相差数据。

基于一元回归方程的最小二乘算法得到了[a,][b]的估计值,其中,[a]为本地晶振产生的秒脉冲相对于GPS秒脉冲的初始误差,[b]为晶振秒脉冲每秒相对于GPS秒脉冲产生的频偏。从以上采集到的数据及[a,][b]估计值计算可知,本地晶振在补偿前相对于标准频率(以GPS为参考)的准确度为10-5,补偿后其准确度为10-8,且晶振频偏相对于标准频率具有很好的线性关系,通过调整晶振的分频系数,可有效提高晶振秒脉冲的准确性。

图7,图8给出了示波器在晶振秒脉冲校正前后观察到的波形。Ch1为GPS秒脉冲上升沿,Ch2为晶振秒脉冲上升沿,Ch3为相差。

从波形图看出,补偿之前,GPS与晶振秒脉冲在某时刻差约340 ms,并且这个差值因为晶振的漂移和其他误差的影响而不断增大。此时,单片机处于接收相差数据阶段,一旦达到其预定接收数值要求,单片机依据回归方程算出需要补偿的数值,对晶振时钟误差进行修正。从补偿的结果看,晶振秒脉冲和GPS秒脉冲的同步精度优于200 ns。

5 结 语

通过GPS自动定时校频,设计了数字式频率合成的高精度晶振时标。通过采用频率补偿方法,使本地普通晶振产生的时钟准确度由10-5提高到了10-8,获得了较好的补偿效果。守时性能主要取决于晶振的稳定性,若要提高守时性能,只需要在电路中采用更高稳定度的频率标准即可达到目标。

参考文献

[1] 张斌,张东来.基于GPS的高精度时钟在线校频与授时研究[J].中国电机工程学报,2012,32(10):160?167.

[2] 蓝波,胡修林.一种高精度系统时间同步方法[J].信息与控制,2011,40(3):61?65.

[3] 李二鹏,文开章,冯保红,等.石英晶体振荡器频率特性的测量与分析[J].测控技术,2010,29(1):81?83.

[4] NAOTO K, MASAHIRO S, TOHRU M, et al. Monitoring of interarea oscillation mode by synchronized phasor measurement [J]. IEEE Transactions on Power Systems, 2006, 21(1): 260?268.

[5] 刘利辉,增建平.100 MHz低噪声恒温石英晶体振荡器研制[J].湖南大学学报,2009,36(7):53?56.

[6] 费业泰.误差理论与数据处理[M].6版.北京:机械工业出版社,2010.

[7] 马凤鸣.时间频率计量[M].北京:中国计量出版社,2009.

[8] 吴继华.Altera FPGA/CPLD设计(高级篇)[M].2版.北京:人民邮电出版社,2011.

[9] 苗苗,周渭,刘晨,等.用于时间同步的高精度短时间间隔测量方法[J].北京邮电大学学报,2012,35(4):49?51.

[10] 蔡振江.单片机原理及应用[M].北京:电子工业出版社,2011.

系统上电后,复位信号对24位计数器、24位预置值寄存器清零。以GPS秒脉冲上升沿作为首次计数的同步信号,开始对本地晶振计数。24位计数器计数值与预置初始频率值(11 059 200 Hz)比较,若不相等,继续完成计数操作,若两者相等,则对计数器清零,重新开始计数,这样通过对晶振分频就得到了本地秒脉冲信号。

由于晶振存在漂移误差,本地产生的秒脉冲不可避免的与GPS秒脉冲存在相位差,鉴相及相差计数电路每秒都会对两者的相位差进行提取并计数。一旦采集的相差数据达到单片机需要的数据量(在本系统中设计提取相差数据量为20个),则单片机采用最小二乘法对得到的数据进行统计计算,得到补偿后的频率值,并通过预置值寄存器送入CPLD,实现晶振频率修正。图3为用示波器观测到的波形。Ch1通道为GPS接收机输入的秒脉冲,Ch2通道为晶振产生的秒脉冲波形,Ch3通道为数据传输中断请求信号。

2.2 鉴相与相差计数电路设计实现

鉴相电路主要将GPS秒脉冲和晶振秒脉冲的相位差信号提取出来,作为相差计数电路的闸门信号。这里设计了3D鉴相器完成这一功能。

3D鉴相器使用3个D触发器和1个2选1选择器构成,以GPS信号作参考,分别在晶振秒脉冲前沿超前、滞后的情况下,以选择器A端、B端作为输出,S端作为晶振秒脉冲相位变化的标志。其电路组成如图4所示。时序仿真图如图5所示。

相差计数电路采用闸门法[9],以晶振脉冲作为计数填充脉冲对相差信号计数,并将计数结果保存在存储器中。晶振秒脉冲下降沿中断触发信号触发单片机响应中断,将相差数据读入单片机的内存单元,然后向CPLD计数器发出清零信号,对相差计数器清零,等待下一个相差信号的到来。

3 算法设计

软件设计所用器件为P89C51单片机,开发环境为Keil C51[10]。单片机实现最小二乘算法,具体实现方法如下:单片机接收相差数据到其设定数值时,将得到的数据按一元线性数理统计模型进行计算[3,6],得到模型系数[a,b]的估计值和需要补偿的计数值,通过数据总线将修正值送入CPLD的存储器修正晶振秒脉冲输出。单片机完成算法流程见图6。

4 相差数据算法处理及修正结果

表1给出了单片机实际采集到的一组相差数据。

基于一元回归方程的最小二乘算法得到了[a,][b]的估计值,其中,[a]为本地晶振产生的秒脉冲相对于GPS秒脉冲的初始误差,[b]为晶振秒脉冲每秒相对于GPS秒脉冲产生的频偏。从以上采集到的数据及[a,][b]估计值计算可知,本地晶振在补偿前相对于标准频率(以GPS为参考)的准确度为10-5,补偿后其准确度为10-8,且晶振频偏相对于标准频率具有很好的线性关系,通过调整晶振的分频系数,可有效提高晶振秒脉冲的准确性。

图7,图8给出了示波器在晶振秒脉冲校正前后观察到的波形。Ch1为GPS秒脉冲上升沿,Ch2为晶振秒脉冲上升沿,Ch3为相差。

从波形图看出,补偿之前,GPS与晶振秒脉冲在某时刻差约340 ms,并且这个差值因为晶振的漂移和其他误差的影响而不断增大。此时,单片机处于接收相差数据阶段,一旦达到其预定接收数值要求,单片机依据回归方程算出需要补偿的数值,对晶振时钟误差进行修正。从补偿的结果看,晶振秒脉冲和GPS秒脉冲的同步精度优于200 ns。

5 结 语

通过GPS自动定时校频,设计了数字式频率合成的高精度晶振时标。通过采用频率补偿方法,使本地普通晶振产生的时钟准确度由10-5提高到了10-8,获得了较好的补偿效果。守时性能主要取决于晶振的稳定性,若要提高守时性能,只需要在电路中采用更高稳定度的频率标准即可达到目标。

参考文献

[1] 张斌,张东来.基于GPS的高精度时钟在线校频与授时研究[J].中国电机工程学报,2012,32(10):160?167.

[2] 蓝波,胡修林.一种高精度系统时间同步方法[J].信息与控制,2011,40(3):61?65.

[3] 李二鹏,文开章,冯保红,等.石英晶体振荡器频率特性的测量与分析[J].测控技术,2010,29(1):81?83.

[4] NAOTO K, MASAHIRO S, TOHRU M, et al. Monitoring of interarea oscillation mode by synchronized phasor measurement [J]. IEEE Transactions on Power Systems, 2006, 21(1): 260?268.

[5] 刘利辉,增建平.100 MHz低噪声恒温石英晶体振荡器研制[J].湖南大学学报,2009,36(7):53?56.

[6] 费业泰.误差理论与数据处理[M].6版.北京:机械工业出版社,2010.

[7] 马凤鸣.时间频率计量[M].北京:中国计量出版社,2009.

[8] 吴继华.Altera FPGA/CPLD设计(高级篇)[M].2版.北京:人民邮电出版社,2011.

[9] 苗苗,周渭,刘晨,等.用于时间同步的高精度短时间间隔测量方法[J].北京邮电大学学报,2012,35(4):49?51.

[10] 蔡振江.单片机原理及应用[M].北京:电子工业出版社,2011.