...MATLAB的FIR数字滤波器的设计

郭广浩 刘志哲 孟庆龙 马承光

摘 要: 在雷达接收、语音图像处理、模式识别、无线通信等领域,数字滤波器已经成为重要组成部分。通过分析和研究FIR数字滤波器的结构特点,结合实际的工程实践需求,设计了一种多级并行流水FIR数字滤波器,并提出了一种精确而又简便的冲击响应系数的量化方法,即基于最小冲击响应系数按等比例量化的方法。这种方法不仅可以根据具体的设计要求随意更改设计位宽,还能保障设计的精度。通过编写Verilog HDL 进行了设计实现,Modelsim仿真与Matlab仿真对比结果表明,各项参数均满足设计要求。

关键词: FIR数字滤波器; 多级并行流水; 等比例量化; 设计与验证

中图分类号: TN713?34 文献标识码: A 文章编号: 1004?373X(2015)01?0069?04

Abstract: The digital filter has become an important part in the radar receiving, voice and image processing, pattern recognition, wireless communication and so on. Based on analysis and research on the structure characteristics of FIR digital filter, a multilevel parallel pipeline FIR digital filter was designed in combination with actual demand of engineering. A precise and simple quantification method of impulse response coefficient is proposed in this paper, that is, the method based on the minimum impulse response coefficient and according to the equal proportion quantification. This method not only can change the designed bit wide at will according to specific design requirements, but also can guarantee the precision of the design. The design was realized by means of Verilog HDL. The results of comparison between Modelsim simulation with Matlab simulation indicate that each parameter meet the design requirements.

Keywords: FIR digital filter; multilevel parallel pipeline; equal proportion quantification; design and verification

0 引 言

数字信号处理已经成为雷达接收、语音图像处理、模式识别、无线通信等领域的关键技术,而数字滤波器则是进行数字信号处理的重要组成部分。有限脉冲响应(FIR)数字滤波器具有很好的稳定性和线性相位特性,在许多实际的电子系统中得到了广泛的应用。由于现代数字信号处理技术需要处理大量的数据,实时性良好和性能高效的数字滤波器对于数字信号处理技术至关重要,本文所设计的多级并行流水FIR数字滤波器,能够达到高速处理大数据率、单周期响应的要求。在数字时代高速发展的今天,开展此类高性能FIR数字滤波器的研究和设计不仅对信号处理领域具有非常重要的意义,而且对其相关联的技术领域也有十分重要的推动意义。

1 FIR数字滤波器的基本结构

数字滤波器按照其冲击响应的特点不同可以分为有限脉冲响应(Finite Impulse Response,FIR)和无限冲击响应(Infinite Impulse Response,IIR)数字滤波器,前者是指单位脉冲响应序列[h(n)]为有限长序列,后者是指单位脉冲响应序列[h(n)]为无限长序列。由于FIR良好的幅度频率特性和严格的线性相位特性,使其在很多实际的电子系统中得到了广泛的应用[1]。

根据其网格结构的不同一般可以分为直接型、级联型、线性型、频率采样型等[2?3]。对于线性FIR可以利用其对称性来简化网格结构(这里只讨论偶对称的情况,奇对称的原理一样)。本设计是[N=]偶数的偶对称,其网格结构如图1所示。

2 多级并行流水结构的实现

其电路结构示意图如图2所示。

对于FIR的并行运算来说,可以利用奇偶对称和划分多个部分来共同实现。利用奇偶对称特性可以有效减少乘法器的使用个数;将求和电路进行有效划分虽然增加了加法器的个数但是并行效率大大增强,同时选择在每一级结果后插入寄存器来实现流水化。其多级并行流水的电路结构如图3所示。

其中,输入端A,B分别为对应同一相应系数的寄存器。对于加法运算,两个数相加有可能产生溢出,因此为了避免因溢出而产生的错误,把累加器的位宽根据每加一级增加一位位宽的原则确定,乘法器的位宽就是两个乘数位宽之和。

3 冲击响应系数的量化

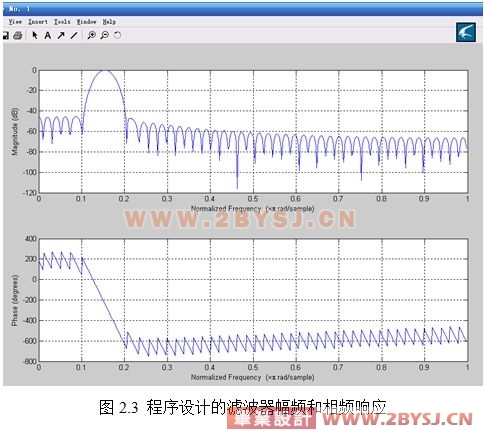

本文设计的滤波器为低通滤波器,其通带截止频率为0.85 kHz,过渡带宽为500 Hz,阻带衰减为60 dB,通带波动为0.1 dB,窗函数为凯赛窗(Kaiser),利用窗函数设计的滤波器阶数为64阶。通过Matlab中的滤波器生成工具,设置好滤波器的参数并生成抽头系数[5]。FIR滤波器的抽头系数多为有符号的小数,必须把它转化为计算机能识别的二进制补码的形式才能进行运算[6]。由于FIR滤波器的系数是无限精度,而实际电路中寄存器的位宽都是有限的,所以必须对无限精度的滤波器系数进行截位或者是舍入。如何对无限精度的滤波器系数进行合理的量化,对滤波器的精度至关重要[7]。

从理论上讲,冲击响应系数和输入的位宽越高,滤波器精度越高,但同时消耗的资源也就越多[8]。研究表明,当量化位数高于16位时,通带内的量化误差的均值小于0.1,能够满足设计需求[9]。为了避免不必要的位宽浪费,同时又保障对精度的要求,本文设计实现了基于最小冲击响应系数按等比例量化的方法,其算法为:

[量化后数据=(量化前数据量化基数)?2N]

其中,量化基数就是冲击响应系数中绝对值最小系数的绝对值;[N]为量化基数的位宽,其表示成二进制的位宽。量化基数的位数越宽,精度就越大。

由于本文设计的输入信号是17位的,综合乘法运算和精度的考量,冲击响应系数选取17位数据。例如本设计中绝对值最大的数除以这个量化基准的值为[1 062.877>210,]因此最少用11位二进制数来表示这个比值。如果用17位二进制数(最高位为符号位,16位数值位)来存储冲击响应系数时,还可以用5位二进制数来表示量化基准,即绝对值最小的数表示成-25 =-32(本设计中绝对值最小的数为负数),这样就能尽量多地存储有效的数据,使其充斥整个存储空间。本设计就是基于这种思想,所有冲击响应系数和量化基准的比值乘以25转化成17位的二进制数之后即可存储,使存储的位宽空间达到满量程。本文设计的实数型冲击响应系数如表1所示,根据系数的对称性只列出一半。

这里量化基数为[h(0)]的绝对值,即0.000 144 516 940 331 9,所有系数除以这个基数再乘以比例基准25就得到设计所用到的量化系数,量化后的32个二进制补码系数如表2所示。

4 仿真结果对比及性能分析

Modelsim的仿真结果如图4所示,din为滤波器输入信号,dout为40位没有经过截位的输出信号。在实际的系统中,对滤波器的输出数据进行适当的截位,能够保障输出数据的相频和幅频特性的同时,还能减少后级所消耗的资源。

用Matlab编写仿真模型,将其输出结果和Modelsim仿真的结果都以文本的形式输出,Matlab运算的输出结果如图5所示,其结果和图4的结果一一对应。将两种结果的文本进行一一比对,结果完全一致,说明其功能正确。

通过Matlab编写的仿真模型来观察仿真结果的频谱图,输入信号为两个频点的有噪声的信号。观察到该多级并行流水FIR数字滤波器对高于1 000 Hz的信号有明显的滤波效果,其截止频率、过渡带宽等性能参数均符合设计要求。该FIR数字滤波器的滤波特性频谱如图6所示。

5 结 语

本文根据实际的工程实践需求,介绍了一种多级并行流水FIR数字滤波器的基本结构和设计实现,并提出了基于最小冲击响应系数按等比例量化的方法,使冲击响应系数的生成更加准确和简单。通过Modelsim仿真结果与Matlab仿真结果的对比,该多级并行流水FIR数字滤波器的各项指标均满足设计要求,能够大大提高系统的处理频率,满足了在高速、大数据量的数字信号系统中处理大数据率、单周期响应的要求。

参考文献

[1] 张登奇,李望移.基于Matlab的FIR数字滤波器设计[J].计算机时代,2007(11):47?49.

[2] 华玲,常建平.高阶FIR滤波器的计算机设计与FPGA实现[J].现代电子技术,2011,34(2):99?102.

[3] 李书华,曾以成.基于分布式算法的高阶FIR滤波器及其FPGA实现[J].计算机工程与应用,2010(12):136?138.

[4] 丁玉美,高西全.数字信号处理[M].2版.西安:西安电子科技大学出版社,2000.

[5] 王旭东,勒雁霞.Matlab及其在FPGA中的应用[M].2版.北京:国防工业出版社,2008.

[6] 刘仲,陈跃跃,陈海燕.支持任意系数长度和数据类型的FIR滤波器向量化方法[J].电子学报,2013,41(2):346?351.

[7] 杜勇,路建功,李元洲.数字滤波器的Matlab与FPGA实现[M].北京:电子工业出版社,2012.

[8] MIRZAEI S, HOSANGADI A, KASTNER R. FPGA implementation of high speed FIR filters using add and shift method [C]// Proceedings of 24th International Conference on Computer Design. San Jose, California: IEEE, 2006: 308?313.

[9] 戴曜泽,王春雷,朱智强.基于FPGA高阶FIR滤波器的实现[J].现代电子技术,2012,35(8):110?113.